電磁兼容EMC基礎知識和實用的PCB設計技巧

雖然經常用作同義詞,但電磁兼容性(EMC)實際上是輻射和傳導電磁干擾(EMI)的控制; 而糟糕的EMC是PCB重新設計的主要原因之一。實際上,估計有50%的首次運行的電路板發生故障,因為它們要么發出不需要的EM和/或對它敏感。這很可能是因為某些行業(例如醫療和航空航天)的嚴格法規,或者因為正在開發的產品要加入歷史上一直考慮EMC設計的產品線。例如,移動電話開發人員生活和呼吸無線連接,并且精通小化不必要輻射的風險。

EMC問題嚴重的是那些用于白色家電的PCB的設計者 - 例如烤面包機,冰箱和洗衣機 - 它們加入了與物聯網無線連接的眾多互聯網設備,由于涉及的產品產量大,重新設計PCB可能會導致產品發布延遲。更糟糕的是,產品召回可能會對公司的聲譽和財務造成嚴重損害。

所以產品設計之初就綜合考慮周全EMC問題,會給您的產品設計節省很多費用!

噪音來自哪里?

考慮到EMC的設計并不缺乏指導,許多公司都有自己的內部PCB設計和EMC規則,指導也可以來自外部來源,例如立法機構,IC供應商和客戶。但是,以面值接受所有指南可能會導致過度防御的EMC策略,并導致項目延遲。應單獨評估規則以確定它們是否適用于當前設計。

也就是說,自己具備一點EMC設計基本常識對設計會有很大班助,例如,為了抑制PCB上的噪聲源,您應該:

1.保持時鐘頻率盡可能低,上升邊緣盡可能慢(在需求規格范圍內);

2.將時鐘電路放置在電路板中央,除非時鐘必須離開電路板(在這種情況下,時鐘必須靠近相關連接器);

3.安裝時鐘晶體與面板齊平并研磨;

4.保持時鐘循環區域盡可能小;

5.將I/O驅動器定位在信號進入/離開板的點附近;和

6.過濾所有進入板的信號。

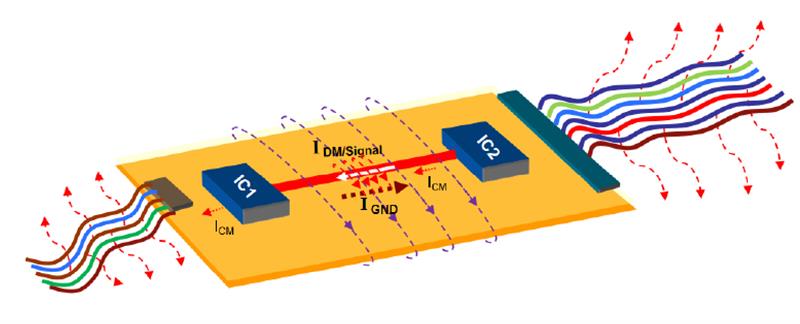

雖然上述措施將有助于緩解一些常見的EMI問題,但每個有源PCB仍將輻射EM能量。這是因為每個電流都產生磁場,每次充電都會產生電場。總輻射將是信號環路差模輻射,共模輻射(電壓和電流驅動)和配電系統(PDS)產生的輻射之和。

你應該更詳細地研究這些:

1、差模輻射是由傳輸線環路引起的,信號產生的是差分電流(見圖1)。對策包括使用屏蔽層(Vcc或接地),在內層放置關鍵信號(也稱為條帶線),避免信號的長并行運行,如上所述,小化環路面積并保持信號上升和下降時間與可能。

圖1:差模輻射

2、共模輻射通常是更為關鍵的EMC設計方面,因為EMI在遠場中更“可見”。它由寄生電流(例如,通過磁通耦合的開關電流或感應電流)或寄生電壓(例如到有源IO信號的串擾電壓)產生。對策包括去除那些寄生電流和電壓的來源 - 從而避免快速切換信號之間的串擾 - 以及更智能的元件布局和布線,以避免磁通耦合和包裹效應。

圖2:共模輻射

3、對于PDS,它可以輻射,因為PCB本質上是一個LCR諧振器,包括電感元件(軌道),電容(接地和電壓平面就像電容器的極板)和電阻。PDS EMI的對策包括降低電路板阻抗,避免電感并確保足夠的去耦。

此外,IC也是EMI的來源,并將有助于PCB的EM配置文件。在IC選擇期間必須考慮到這一點,芯片供應商應該能夠為您提供有關電路EMI行為的信息。

規則檢查器和模擬

許多PCB設計工具包括EMC規則檢查器,檢查包括查看可能發生信號串擾的實例的設計數據幾何(由于并行路由的跡線),很少或沒有屏蔽的情況,以及可能需要去耦的情況。

這些規則將包含許多EMC工程師的“技術訣竅”。但是,了解它們的起源以及CAD工具供應商如何實現它們非常重要; 并且您有權要求查看供應商的規則書。這些工具還應該可以突出顯示EMI抑制和EMC完整性至關重要的PCB區域 - 您可以告訴工具您的優先級。

但是,我們不要忘記,這些都是布局后檢查。好以EMI和EMC為設計理念,而不是進行試錯練習。此外,如果有任何可能的EM輻射水平,您將收到很少的指導。

要進行更高級的分析,需要進行模擬,與EMC設計規則檢查器一樣,結果的意義和價值將取決于電路板的數字表示及其行為的呈現程度,當然還有各種EM方程作為軟件算法實現的程度。同樣,工具供應商應該能夠提供信息。您還應該采取一些有代表性的測量來驗證模擬方法,并編制指標作為解釋未來結果的基礎。

市場上有許多數字3D EM仿真工具,其中一些專用于天線設計等特定活動,它們非常適合假設研究和結構優化。他們可以為給定結構建模所有EMI效應,但它們確實需要相當大的計算能力(內存和CPU時間),并且往往會花費很多。此外,需要深入了解EMI以理解結果,因為有時難以單獨使用3D EM結果來解釋特定輻射峰值的原因。

但是,對于白色家電中使用的PCB類型,我們并不尋求優化天線結構或產生特定的射頻曲線; 我們只是希望驗證電路板設計是否具有良好的EMC - 并且具有良好EMC規則檢查器的PCB設計CAD工具就足夠了。

如何設計電磁干擾EMI?

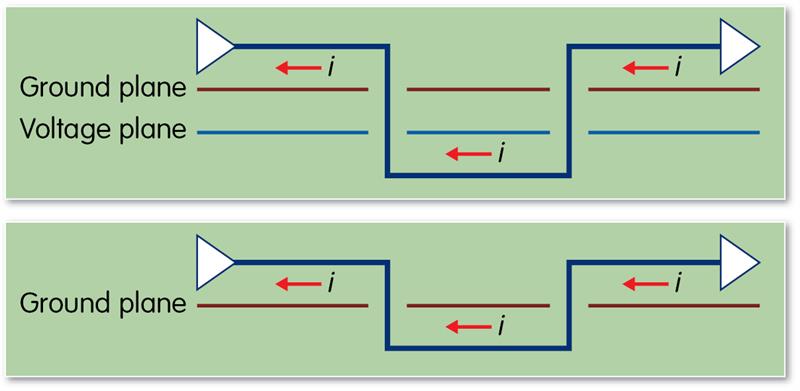

盡管EMC沒有靈丹妙藥,但良好的設計工作應包括識別寄生EMI天線,如電偶極子。此外,識別當前路徑,因為電流在循環中流動并始終尋找阻力小的路徑。因此,計劃適當的返回路徑(注意'地面'不是EMC工程中可接受的技術術語)并避免交叉分裂/間隙(即使是差分對)和返回路徑不連續(見圖3)。

圖3:在頂部圖中,參考層從地平面變為電壓平面,用于部分跡線。這產生了EMI天線。保持相同的參考平面,如下圖所示,避免/減少返回路徑的不連續性。

總而言之,好以EMC為設計目標,而不是冒險重新設計電路板,但您必須清楚地了解哪些EMC規則適用于您的項目。此外,在PCB設計CAD工具中嵌入EMC分析功能可以在制造電路板后大大降低EMC合規性失敗的風險; 但請確保該工具的規則檢查程序基于經過充分記錄和驗證的EMC原則和解釋。除非a)您信任模擬器并且b)您對結果的感受有所了解,否則永遠不要模擬。

環測威主要幫客戶解決電磁兼容性測試問題,涉及到電磁兼容emc的整改,FCC無線認證等!

詳情咨詢工程師:4008-707-283

閱讀本文的人還閱讀了: